- 您现在的位置:买卖IC网 > Sheet目录346 > NCP5021MUTXG (ON Semiconductor)IC WHITE LED DVR HV AMB 16-UQFN

�� �

�

NCP5021�

�Registers� Setup� Selection�

�The� register� selection� follows� the� I2C� address� of� a� new�

�frame� and� must� be� followed� by� the� DATA� register.� The�

�content� of� the� register� selection� byte� is� not� stored� into� the� chip�

�and� a� new� one� shall� be� send� for� every� DATA� update.� The� low�

�nibble� contains� the� selected� register� number� as� depicted� in�

�Table� 7.� The� high� nibble� is� reserved� for� future� use.�

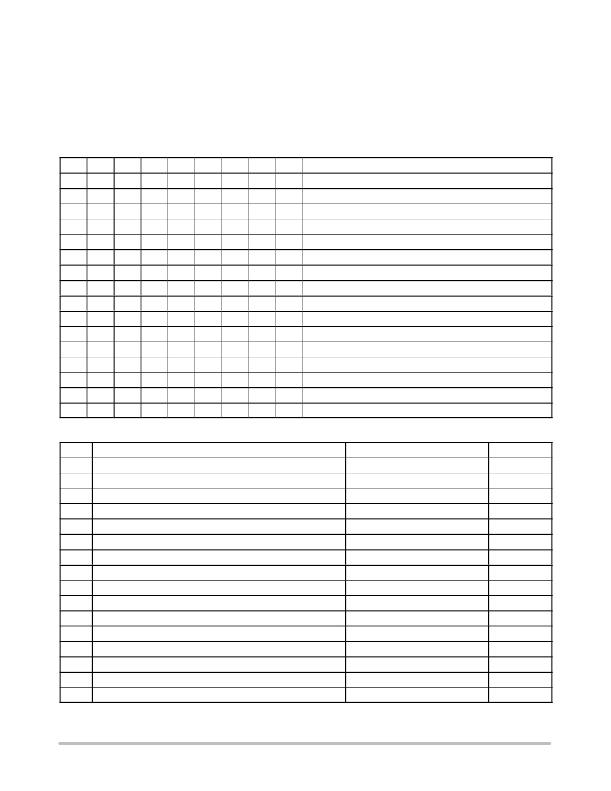

�Table� 7.� REGISTER� SELECTION� CODE�

�The� last� code� $0F� is� reserved� for� ON� Semiconductor� to�

�control� the� manufacturing� test� and� access� to� this� register� is�

�not� permitted� outside� the� ON� Semiconductor� final� test�

�facilities.�

�$�

�B7�

�B6�

�B5�

�B4�

�B3�

�B2�

�B1�

�B0�

�00�

�01�

�02�

�03�

�04�

�05�

�06�

�07�

�08�

�09�

�0A�

�0B�

�0C�

�0D�

�0E�

�0F�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�1�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�0�

�0�

�0�

�0�

�1�

�1�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�0�

�1�

�1�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�1�

�0�

�1�

�Shut� Down� the� chip�

�Select� I� ?� LED� current� setup� and� immediate� LED� update�

�Set� ILED� target� and� Gradual� Dimming� UPWARD�

�Set� ILED� target� and� Gradual� Dimming� DOWNWD�

�Set� timing� and� start� the� gradual� dimming�

�Reserved� for� future� use�

�Reserved� for� future� use�

�Reserved� for� future� use�

�Set� up� Photo� sense� input� stage� gain�

�Set� up� Photo� Sense� I� ?� LED� minimum� value�

�Set� up� Photo� Sense� up/down� timing�

�Reserved� for� future� use�

�Reserved� for� future� use�

�Reserved� for� future� use�

�Reserved� for� future� use�

�Reserved� for� manufacturing� test:� do� not� access�

�Table� 8.� REGISTERS� IDENTIFICATION�

�DEC�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�16�

�Register� Functions�

�Shut� Down� the� chip�

�Select� I� ?� LED� current� setup� and� immediate� LED� update�

�Select� I� ?� LED� target� Gradual� Dimming� command� UP�

�Select� I� ?� LED� target� Gradual� Dimming� command� DOWN�

�Set� Timing� &� Start� gradual� Dimming� Sequence�

�Reserved� for� future� use�

�Reserved� for� future� use�

�Reserved� for� future� use�

�Set� up� Photo� sense� input� stage� gain�

�Set� up� Photo� Sense� I� ?� LED� minimum� value�

�Set� up� Photo� Sense� timing�

�Reserved� for� future� use�

�Reserved� for� future� use�

�Reserved� for� future� use�

�Reserved� for� future� use�

�Reserved� for� manufacturing� test:� do� not� access�

�Register� Identification�

�SDN�

�ILEDREG[4..0]�

�GDIM[4..0]�

�GDIM[4..0]�

�TDIM[4..0]�

�PHGAIN[4..0]�

�PHMIN[3..0]�

�PHCLK[5..0]�

�FTEST[7..0]�

�Command�

�$00�

�$01�

�$02�

�$03�

�$04�

�$08�

�$09�

�$0A�

�$0B�

�$0C�

�$0D�

�$0E�

�$0F�

�http://onsemi.com�

�9�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

NCP5050MTTXG

IC LED DRIVR PHOTO FLASH 10-WDFN

NCP5111DR2G

IC DRIVER HI/LOW SIDE HV 8-SOIC

NCP5304DR2G

IC DRIVER HI/LOW SIDE HV 8-SOIC

NCP5355DG

IC DRVR SYNC BUCK MOSF 12A 8SOIC

NCP5359ADR2G

IC MOSFET GATE DVR DUAL 8-SOIC

NCP5359DR2G

IC GATE DRIVER VR11.1/AMD 8-SOIC

NCP5360RMNR2G

IC DRIVER MOSFET 56QFN

NCP5366MNR2G

IC DRIVER MOSFET DFN

相关代理商/技术参数

NCP502ASQ15T1

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq Voltage Regulator in an SC70−5

NCP502ASQ15T1G

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq, Low−Dropout Voltage Regulator

NCP502ASQ18T1

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq Voltage Regulator in an SC70−5

NCP502ASQ18T1G

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq, Low−Dropout Voltage Regulator

NCP502ASQ25T1

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq Voltage Regulator in an SC70−5

NCP502ASQ25T1G

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq, Low−Dropout Voltage Regulator

NCP502ASQ27T1

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq Voltage Regulator in an SC70−5

NCP502ASQ27T1G

制造商:ONSEMI 制造商全称:ON Semiconductor 功能描述:80 mA CMOS Low Iq, Low−Dropout Voltage Regulator